神经网络的FPGA实现之坑三:基于HDL Coder的DDR4接口模型详解

MATLAB HDL Coder自动生成Arria 10 SoC Development Kit DDR4接口模型详解

由于MathWorks还没有推出针对Intel Altera的DDR接口生成这个demo的解释,在这我们给出一些自己的理解。

MATLAB版本:2018a FPGA硬件平台:Arria 10 SoC Development Kit FPGA软件平台:Intel FPGA 17.0 Standard Edition Simulink模型介绍:

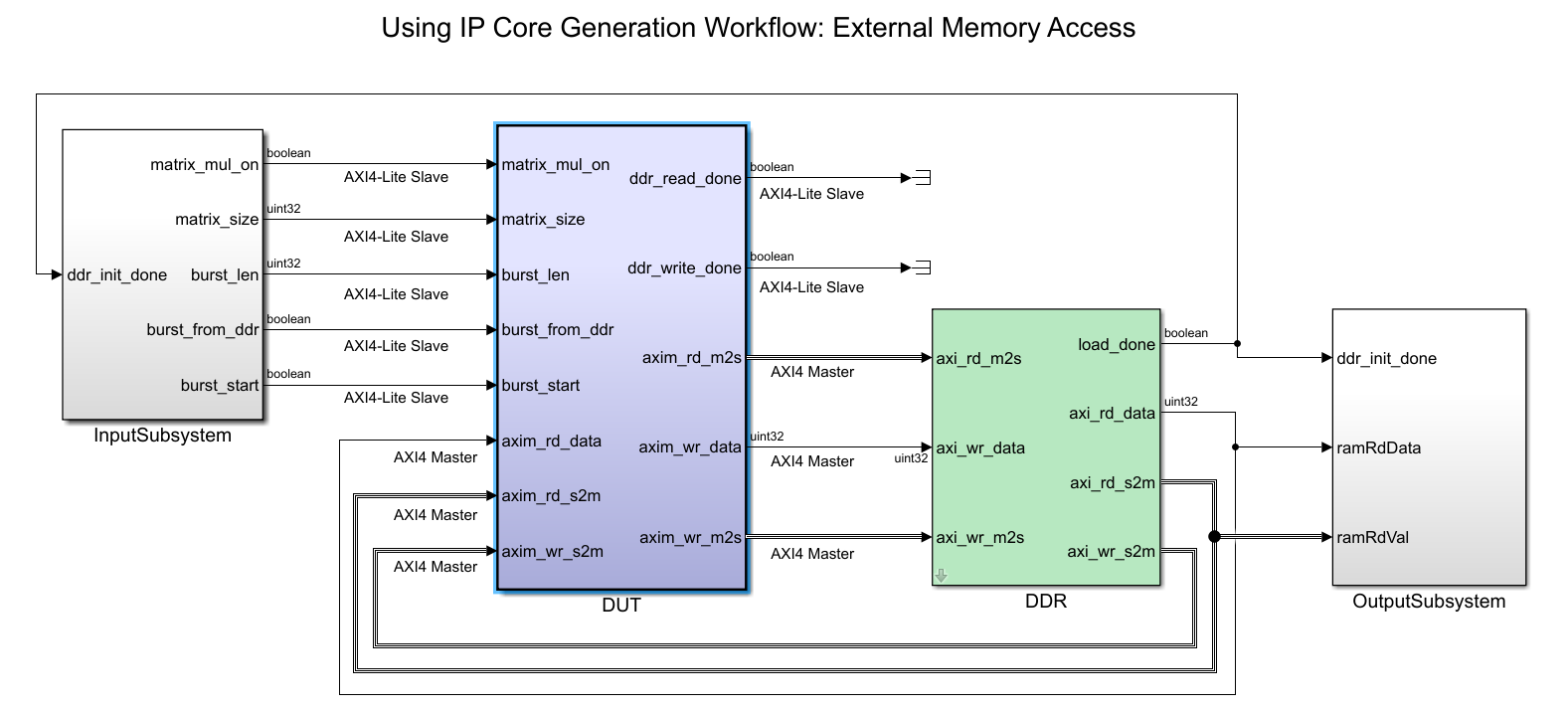

下图给出了Simulink的模型,其中,DUT为未来会转换成HDL的模块

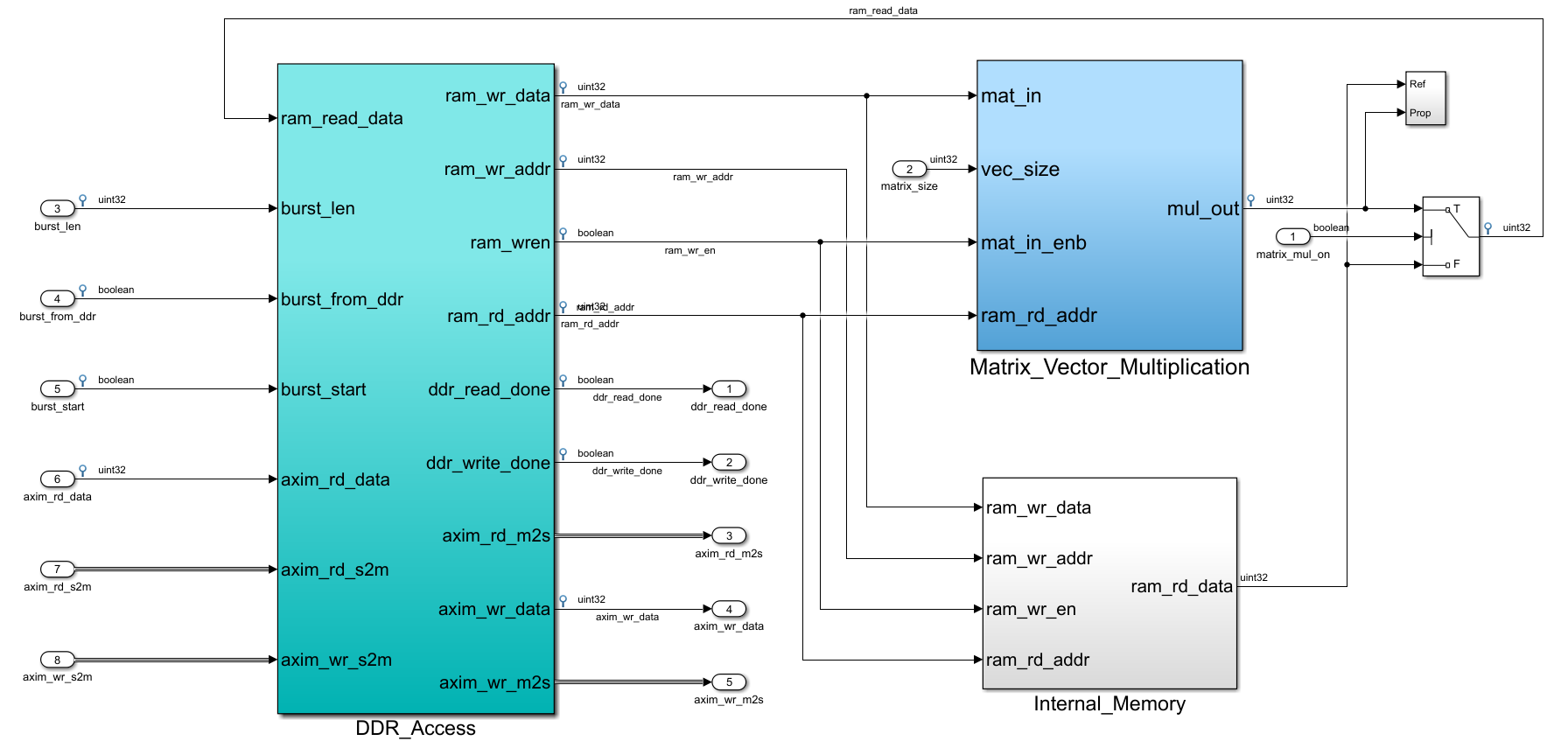

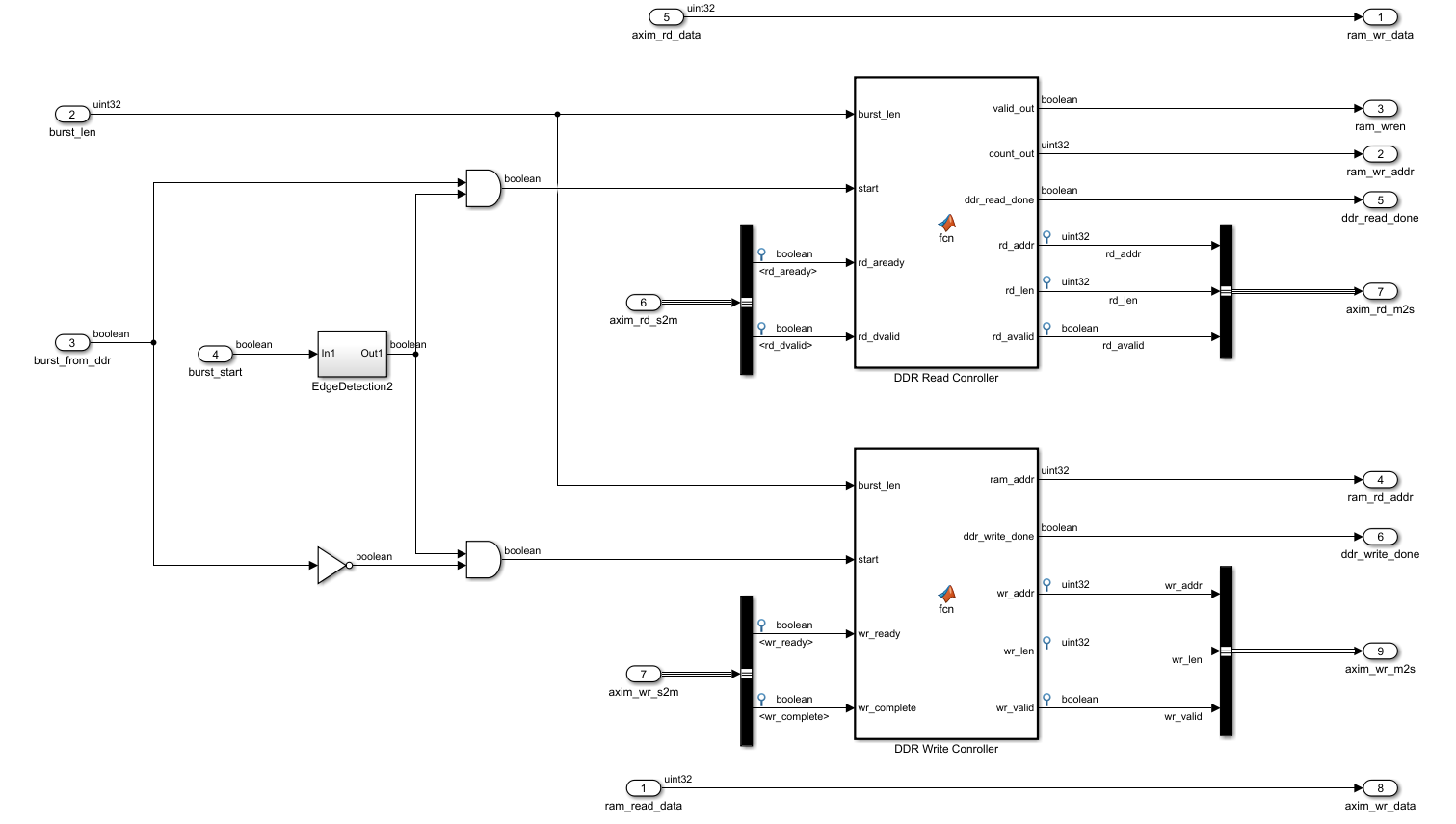

进入DUT模块,可以看到三个模块,DDR_Access(DDRA)、Matrix_Vector_Multiplication(MVM)和Internal_Memory(IM)。

MVM模块实现矩阵和向量的乘法,IM模块用于测试,当matrix_mul_on为F时,MVM的结果不会被写入DDR。下面重点介绍DDRA

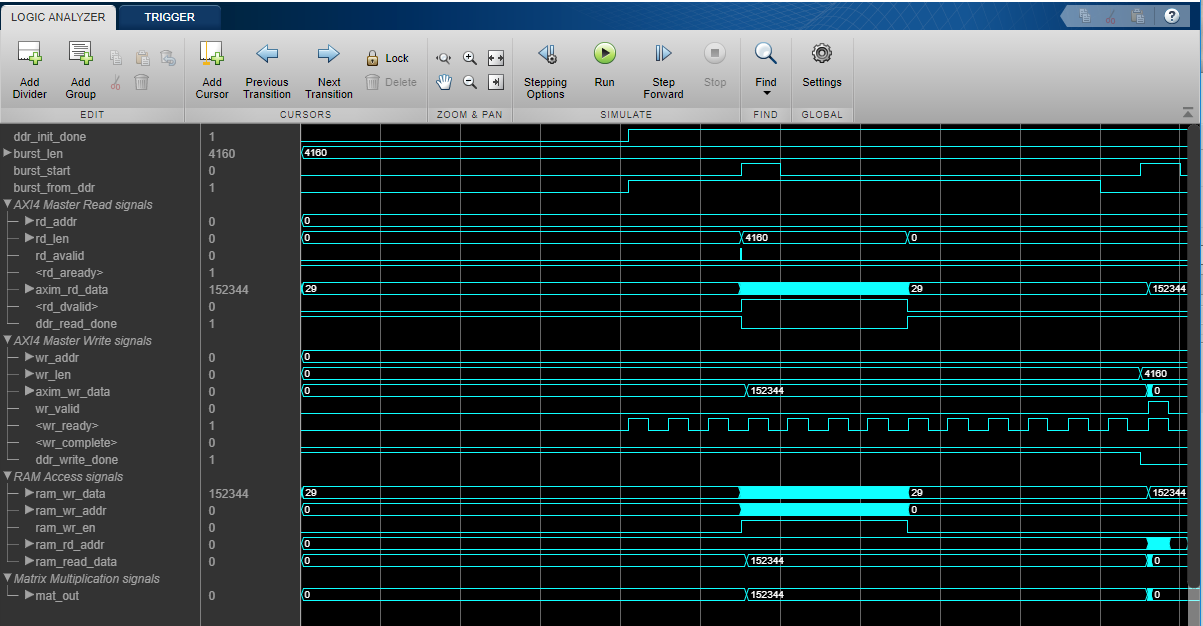

从上图可以看到,axim_rd_data和ram_wr_data直接相连,ram_read_data和axim_wr_data直接相连,也就意味着,写入DDR4的数据也被会写入IM,从IM读出的数据也会被写入DDR4.

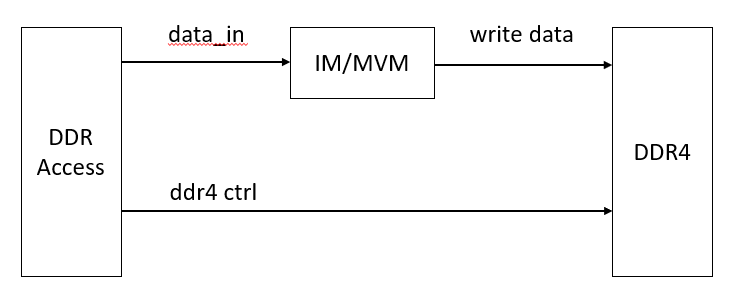

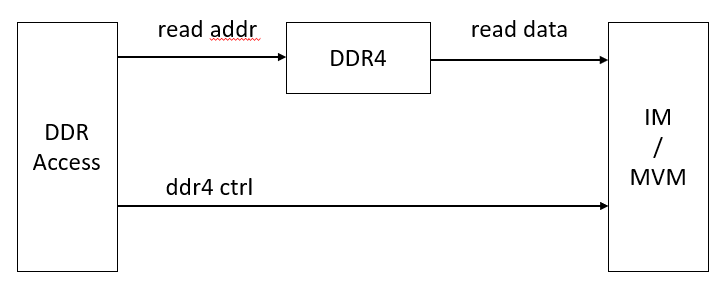

数据通路如下:

用Intel FPGA软件打开RTL Viewer,可以看到

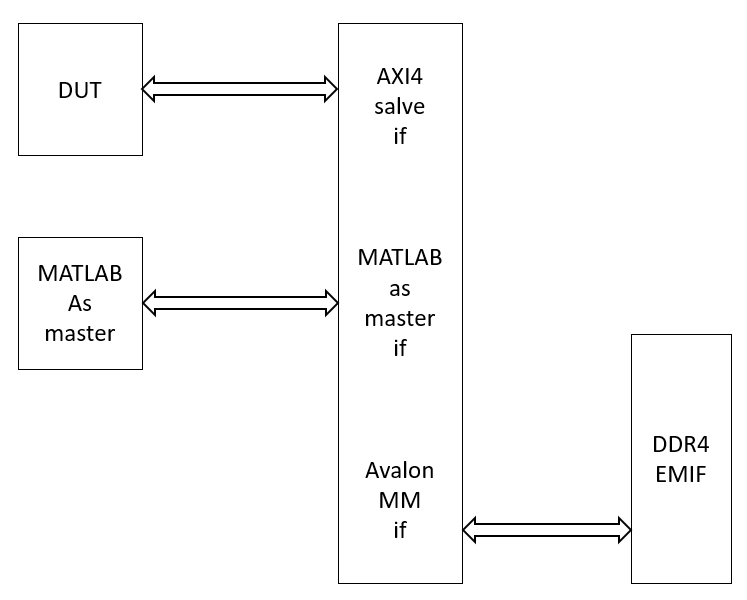

Altera的EMIF(External Memory Interface)使用的是Avalon MM(Memory Mapped)Interface. 上图中间模块起接口转换作用,并且连接了DUT和MATLAB as master模块,给MATLAB提供控制DDR4的接口。

使用DSP Toolbox的Logic Analyzer可以查看波形,单击下图红笔框出的图标,选取Logic Analyzer

参考: